4K DisplayPort Input Functionality for FPGA-based Video Wall Controller, LVDS to SerDes Conversion, Supporting Localized Customization

4K (3840 x 2160 @60Hz) is increasingly becoming a video trend. Integrating 4K into a video wall controller is a challenging problem.

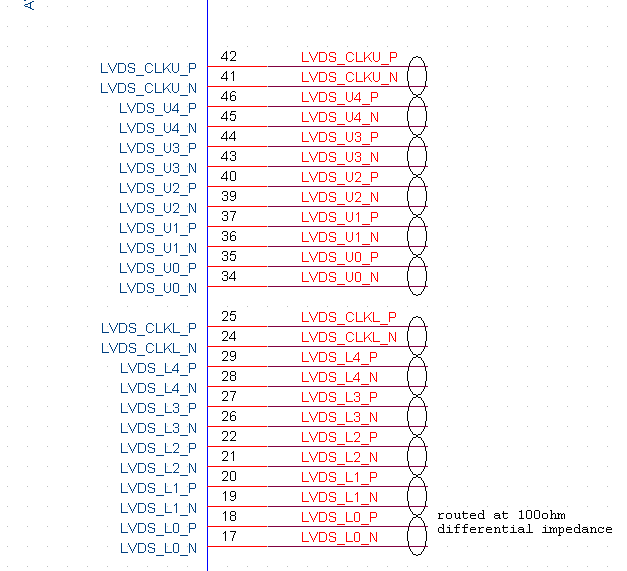

First, let's look at the schematic interface:

This is the LVDS interface of the ANX1122.

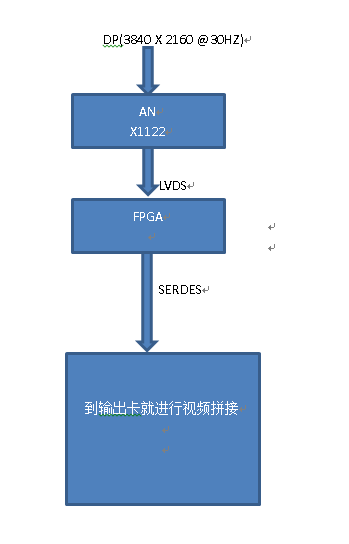

Below is the system block diagram:

The DisplayPort signal enters the ANX1122. The ANX1122 converts the DisplayPort input signal into an LVDS signal. The FPGA then converts the LVDS signal into video timing signals. Finally, the FPGA transmits these timing signals via SerDes.

The output card receives the SerDes signal, converts it back into timing signals, and then performs video wall processing.

Large-screen video wall applications are becoming increasingly widespread. They are found in security monitoring, home theaters, store displays, conference training, and even promotional displays at restaurant entrances. The increasingly common application of large-screen video walls brings broad market prospects.

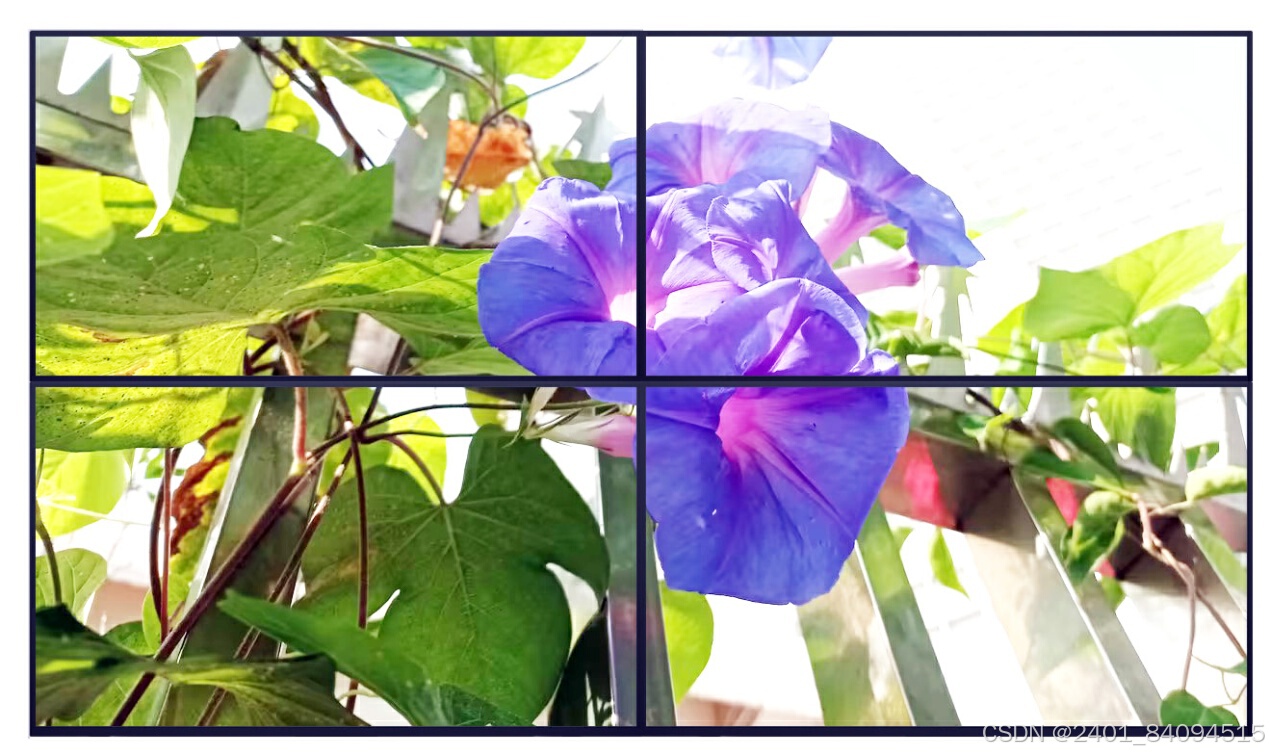

The characteristic of LCD displays is their clear and delicate display. However, the size of individual LCD displays is limited, with mainstream single-screen LCD TVs currently around 100 inches. To create a larger display using LCD panels, video wall technology is required. One drawback of large-screen video walls is that the bezel gaps between screens cannot be completely eliminated. Currently, excellent LCD screens can achieve ultra-narrow bezels of around 0.8mm, providing a very good visual experience. As technology matures and costs decrease, more and more people will choose LCD displays assembled into large-screen video wall products.

Four LCD TVs form a larger video wall.