FPGA-based Design for a Low-Latency 4K 60Hz Video Splicer

Video wall applications are becoming increasingly widespread, found in security monitoring, home theaters, store displays, conference training, and even promotional displays at restaurant entrances, among other venues. The increasingly common application of large video walls brings broad market prospects.

LCD displays are characterized by clear and delicate image quality, but the size of individual LCD displays is limited. Currently, mainstream single-screen LCD TVs are only around 100 inches. If you want to form a larger display using LCD panels, you need to employ screen splicing technology. One drawback of large video walls is that the gaps between screen bezels cannot be completely eliminated. However, current excellent LCD screens can achieve ultra-narrow bezels down to 0.8mm, providing a very good visual effect. With the maturity of technology and the reduction of costs, more and more people are choosing the product form of large displays assembled from LCD panels.

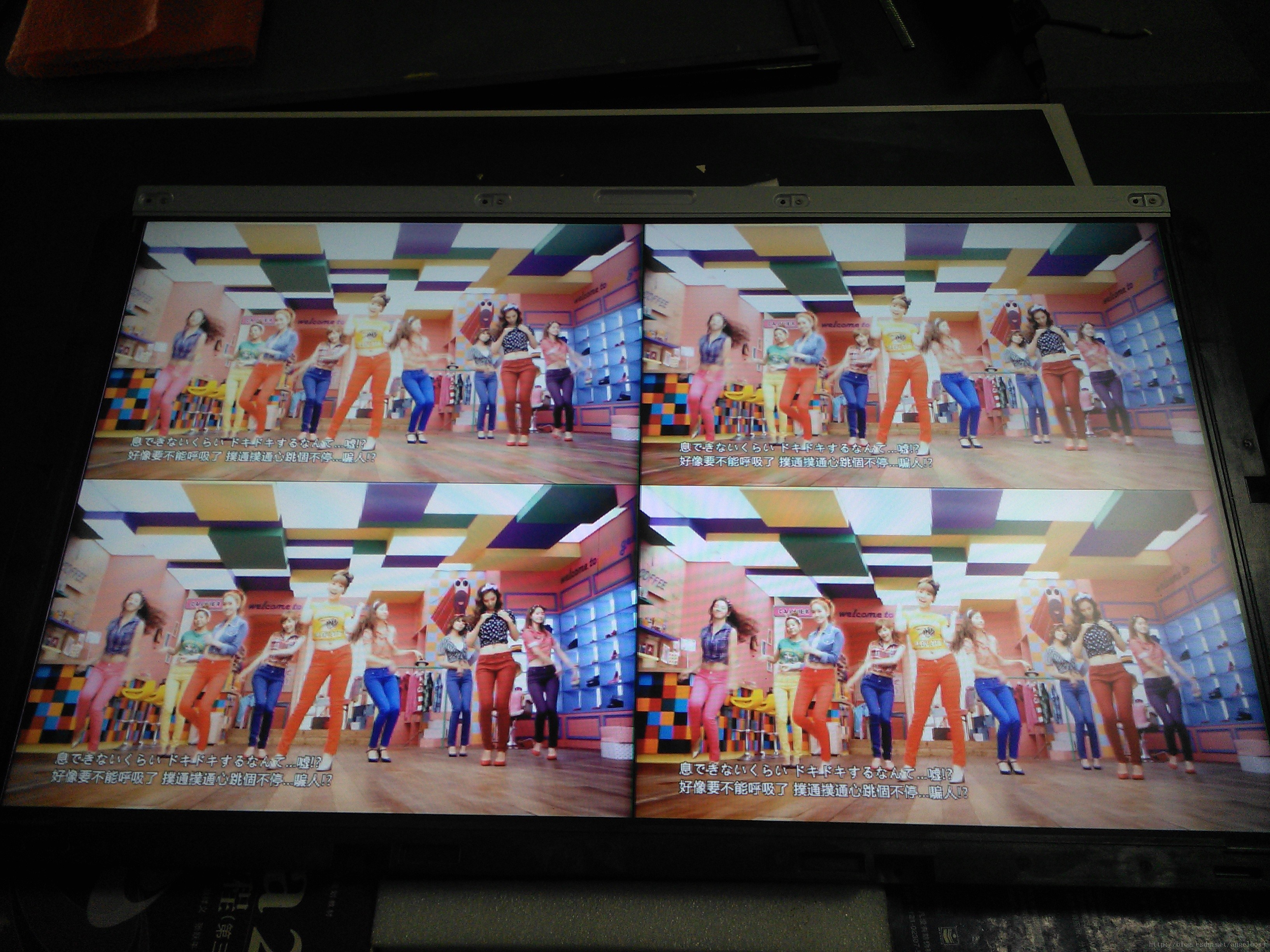

Four LCD TVs form a larger spliced screen.

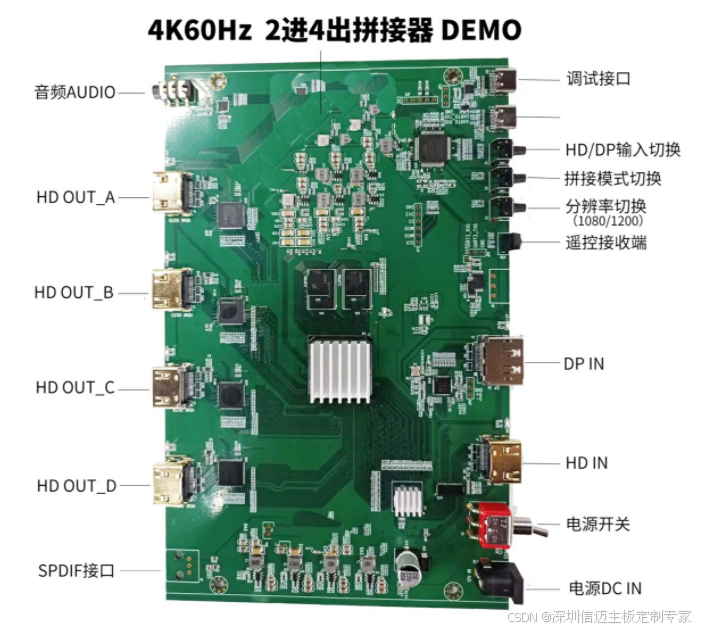

- Supports HD or DP input.

- Supports button, remote control, and RS232 control.

- Supports 2 channels of up to 4K 60Hz ultra-high-definition input (HD or DP).

- Supports 4 channels of up to 1080P 60Hz high-definition output. The total display can be up to 4K 60Hz ultra-high-definition.

- Supports switching between 19201080@60Hz and 19201200@60Hz at the output.

- Compatible with various computer/game console/player devices.

- Supports all display devices with HD interfaces.

- Professional lossless image quality, high color reproduction.

- Supports edge blending.

- Supports 180-degree mirror flip.

- Supports arbitrary swapping of output ports.

- Audio and video synchronization, audio separation.

- Supports custom development for other features.

- Supports the following display modes and resolutions:

The splicer can achieve the following common display modes:

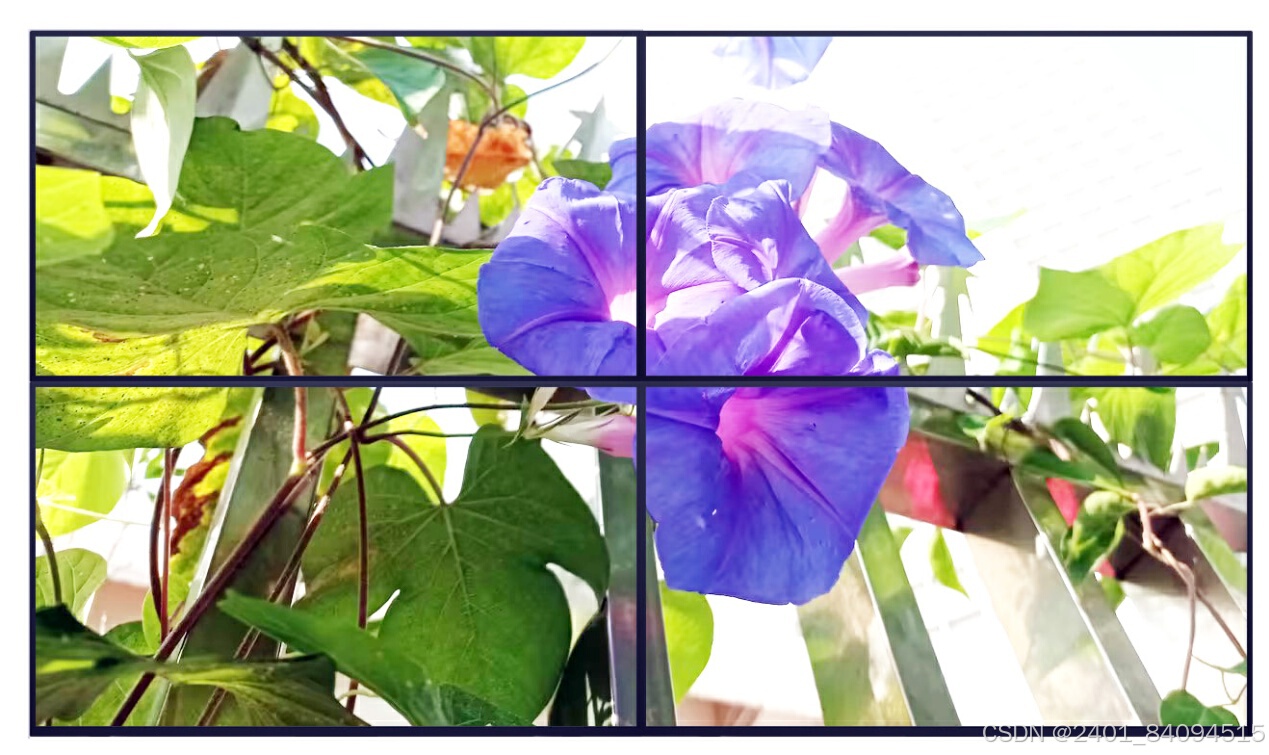

Four-screen mosaic display:

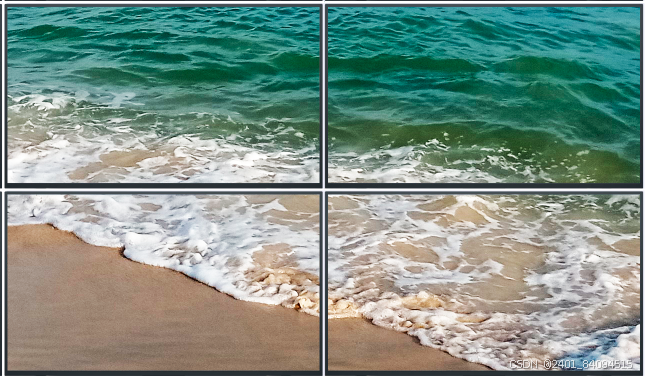

Left-right splicing mode (vertically symmetrical)

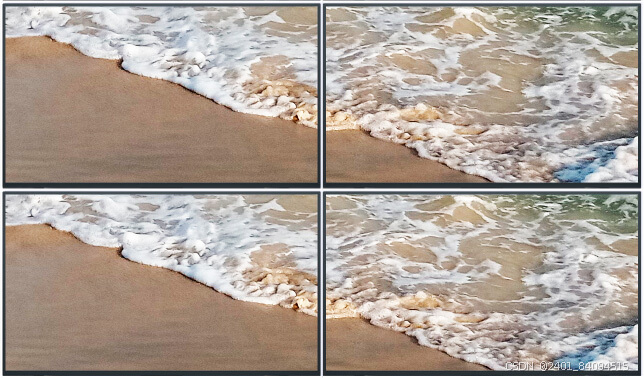

Up-down splicing mode (horizontally symmetrical)

Four-screen vertical display mode (1920x4320 or 1920x4800 resolution)

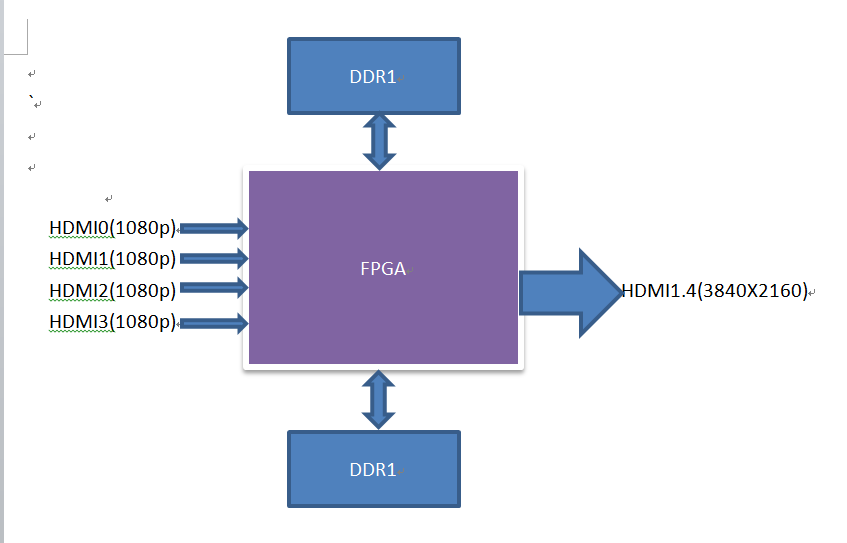

Platform: LATTICE ECP3-70.

Hardware Architecture:

This project primarily aims to synthesize a 4K (3840 x 2160 resolution) video from four 1080P videos.

Project Summary:

For cross-clock domain paths, MultiCycle constraints must be added.

For timing paths that fail, you can wait until the basic functionality is complete, then review the timing report and gradually modify the code to achieve the desired frequency.