x86 Chip Customization, EtherCAT Chip Customization, IP Services, for Motion Control, Industrial Bus, and other Integrated Hardware-Software Systems

x86 Chip Customization, EtherCAT Chip Customization

X86 Platform

Our R&D engineers have accumulated extensive experience in motherboard and complete system design. We can align with your product specification and scenario requirements, and quickly deliver prototypes, including products in various forms such as motherboards, BOX PCs, tablet PCs, and CPCI. Cost reduction, long lifecycle, rapid delivery, and timely response are our strengths.

® Custom Integrated Circuit Services Flexible Services, Complete Solutions Custom Instruction Set Integration System-Level Design Thinking

Leveraging years of technical expertise in industrial computer hardware platform integration and mass production, we offer highly flexible chip design and chip mass production services. We design solutions for clients with a system-level mindset, helping them enhance their competitiveness.

Development Process

XMTECH® ASIC provides comprehensive services and industrial application solutions. Firstly, in terms of design service and mass production, from design, manufacturing to back-end packaging and testing, ® offers tailor-made customized service solutions. In terms of application, depending on different industrial applications such as embedded applications, industrial automation, cloud IoT, etc., ® provides hardware specification design recommendations and ensures hardware-software compatibility from a system perspective, offering clients complete hardware configuration and design. For functional verification, ® provides phased verification methodologies to enhance the completeness of functional verification. For customized projects, from CPU to various peripheral devices, from standard interfaces to special specifications, a rich set of features is offered to help clients design chips for diverse applications. In terms of process technology, from mature processes to advanced processes, ® will consider customer system requirements and cost-effectiveness to achieve optimal performance with the most suitable process. ® provides flexible and comprehensive solutions to help clients strengthen their products and consolidate their market position. ®'s customized R&D process helps clients create the most cost-effective custom chips from a system perspective.

ASIC Service Flow

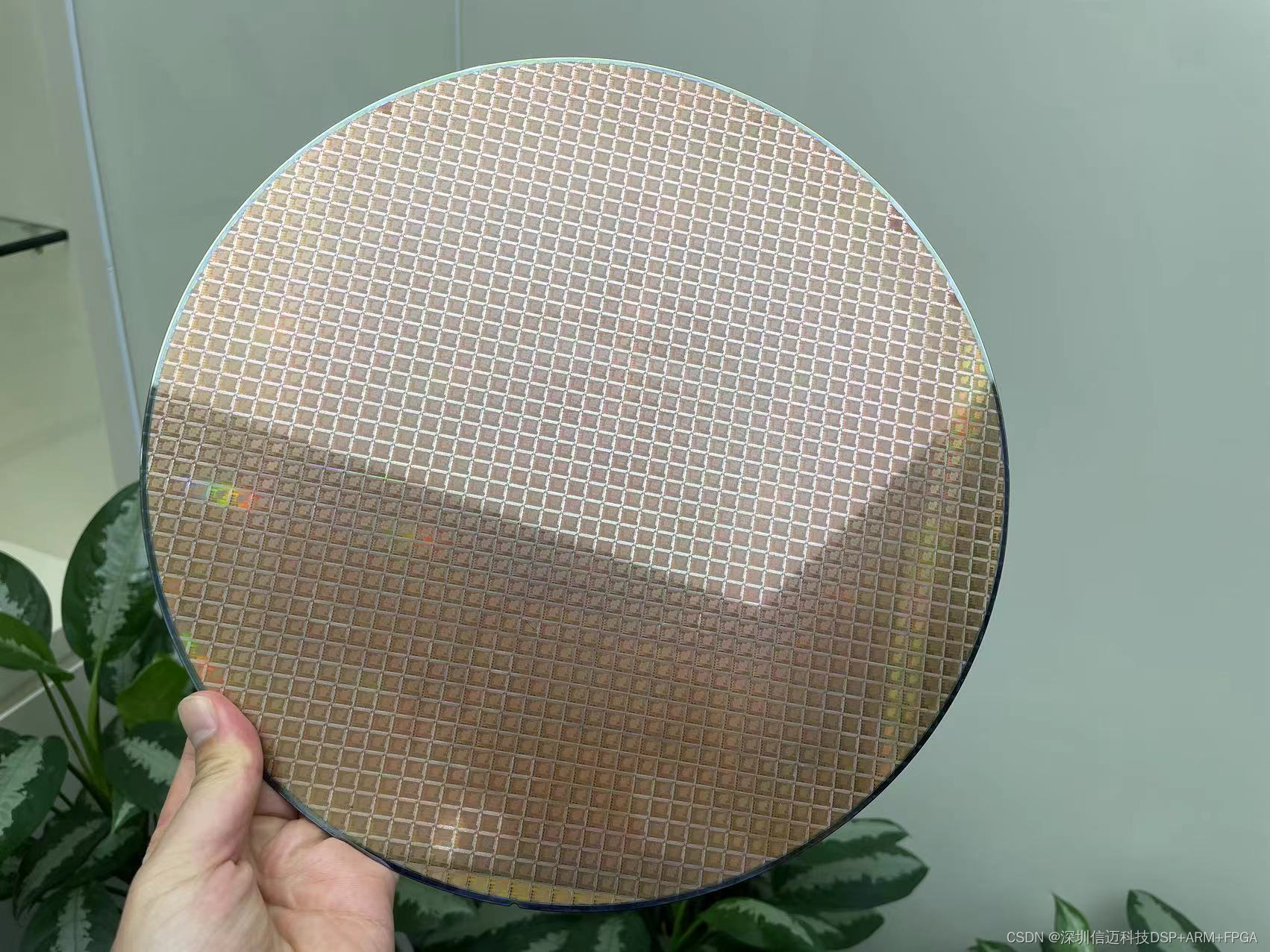

During the specification customization phase, we discuss product applications and specification requirements with clients and provide design recommendations that meet both needs and cost targets. During the chip design phase, we use FPGA test boards for simulation to evaluate performance and optimize the system. During the physical layer design phase, computer-aided software is used to evaluate and optimize power consumption and performance. In the functional verification phase, phased verification methods are provided to enhance verification completeness and reduce verification response time, thereby shortening the R&D cycle. In the chip mass production phase, including wafer production services to chip packaging and testing, we assist clients in optimizing mass production procedures and reducing mass production risks. ® discusses with clients at every stage, listens to their feedback, and provides solutions that best balance cost and performance.

IP Service

Design Specification

- RISC Architecture

- Synchronous Design

- Static Design

- Synthesizable

- Silicon proved (0~66 MHz at 0.5um process)

Key features

-

Instruction compatible with generic 8051

-

256 byte scratchpad RAM interface

-

Two external interrupts

-

Memory Addressing Capability

-

-64K Byte external RAM & ROM

-

8-bit I/O port x 4 (P0~P3)

-

16-bit timer/counter x3

-

Full duplex UART x1

-

Data Pointer x1

-

Watch Dog Timer x1

-

Support Power Down and Idle Mode

-

Power Down waked up by Interrupt

-

12/4/1 clocks/machine cycle (S/T/TT or TTE/TTEX)

-

Dual data pointer (Above T)

Deliverable

- Product Data Specification

- RTL code in Verilog format

- Pipeline Diagram

- Synthesis Script file

- Function Test Pattern in Verilog format

Application

DSC,CF Card, Pattern Recognition, LCD Monitor Controller, USB Device Controller, Scanner Controller, MP3 Controller, Modem Controller, Voice Recognition

Overview

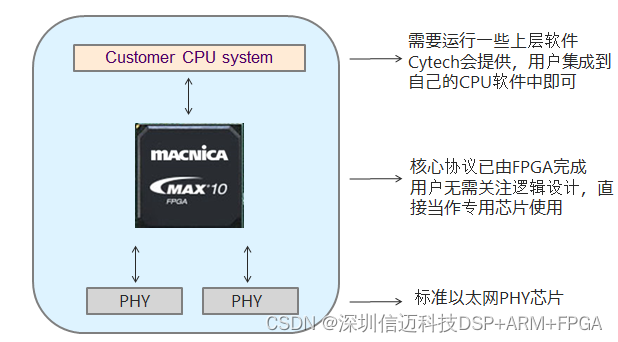

Both commercial EtherCAT master and open-source master implementations achieve master functionality through software. The performance of the master largely depends on the PC's performance and the real-time capabilities of the operating system. However, Xinmai implements the EtherCAT protocol layer using FPGA logic, pre-programmed, so customers can simply use it as a dedicated chip.

The EtherCAT max10 chip implements the standard EtherCAT master protocol. It uses a standard general-purpose parallel bus interface, allowing connection to any CPU for chip control. It supports ARM or x86 processor platforms. Reference software code, API functions, and XML files for system initialization are provided. It can be used to control any standard EtherCAT motors or I/O devices.

Features

- Supports EtherCAT master running on bare-metal programs on ARM processors, without an operating system;

- Supports x86 processors with PCIe interface, providing reference code for drivers and applications under Linux (with Xenomai real-time kernel);

- User-friendly system debugging interface;

- Low CPU load, enabling high real-time performance EtherCAT master communication quickly, regardless of high-end or low-end processors;

- Strong synchronization performance between master and slave, with synchronization time jitter far less than 1us (4-axis measured 50ns);

- Short cycle time, easily achieving a 31.25us communication cycle (a 62.5us cycle can be achieved for 4 axes);

- Easy system configuration via XML files, supporting a large number of slaves.

Performance Comparison