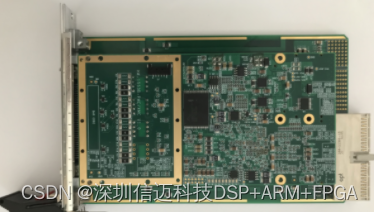

1553B Bus Interface Simulation Card, 1553B IP Core, Applicable to Aerospace Airborne, Integrated Aircraft Avionics, and Other Fields

The 1553B bus interface card can be used as a communication or simulation test board, supporting computer bus platforms such as USB, PCI, PXI, CPCI, Ethernet, RS422, RS485. It offers single-function (1 BC, 0-31 RTs, and 1 BM, currently only single operating mode) and multi-function (1 BC, 0-31 RTs, and 1 BM, currently multiple operating modes available) configurations, with single-channel, dual-channel, triple-channel, and quad-channel options. Communication rates support standard 1Mbps, as well as 4Mbps. Designed for industrial-grade operating temperatures from -40℃ to +85℃, it is rich in features, easy to use, and conducive to secondary development.

The 1553B interface simulation card provides Windows/Linux/VxWorks drivers and supports board diagnostics and testing. It can meet the communication, testing, and simulation requirements for 1553B bus in equipment, laboratories, and field operations.

Key Features:

ØBC Mode

- Supports automatic BC retry

- Supports message inter-message gap setting

- Programmable major frame and minor frame content and transmission timing, message inter-message gap, no-response and delay times

- Message content and operating mode can be modified online

- Provides two message reception methods: interrupt and polling

- Can buffer 2048 processed messages

- Error injection and detection: illegal word, response time, parity check, Manchester encoding/decoding

- Manages messages using a linked list, allowing dynamic addition and deletion of event messages

ØRT Mode

- Supports 0-31 RTs

- Supports independent data caching for sub-addresses

- Programmable error injection, response time, interrupt trigger conditions

- Data, status, and control words can be modified online

- Manages messages using a linked list, allowing dynamic addition and deletion of messages

ØBM Mode

- Uses a circular buffer for data reception

- 100% bus monitoring: error status, word status, message status

- Optional interrupt trigger conditions: RT address, RT sub-address, status or control word, etc.

- Software-configurable monitoring filter conditions, 45-bit time tag

Application Areas:

Ø Aerospace Airborne Electronic Systems

Ø Integrated Aircraft Avionics Systems

Ø Armored Vehicle Integrated Electronic Systems

Ø Naval Vessel Integrated Electronic Systems

Ø Missile and Other Weapon Systems

Ø Building Simulation and Test System Platforms

The 1553B IP core is designed according to the MIL-STD-1553B bus protocol and references the HI-6110 chip. It can be configured to select three operating modes: Bus Controller (BC), Remote Terminal (RT), and Bus Monitor (BM). Input and output command words, status words, and data words are stored via 16-bit registers. Data words are buffered using a FIFO with a depth of 32 and a width of 16 bits. Data transmission encoding uses Manchester code.

Technical Specifications:

Item

Parameter

Functional Indicators

Port Rate

1Mbps, 4Mbps

Number of Ports

Supports 2 redundant input/output channels

Protocol Support

Supports standard BC, BM, RT operating modes

Message Interval

Message interval resolution 1μs

Response Timeout

Software-configurable response timeout: 0-32768μs

Message Transmission

Supports timed transmission of single messages, resolution 1ms

Interface Type

Customizable, provides external register and data transfer interfaces based on HOLT devices

FPGA Support

Xilinx 7 Series FPGAs

Resource Utilization

Registers: 2461

LUTs: 2101

Power Consumption

Logic power consumption approximately 5W

Application Areas:

Ø Aerospace Airborne Electronic Systems

Ø Integrated Aircraft Avionics Systems

Ø Armored Vehicle Integrated Electronic Systems

Ø Naval Vessel Integrated Electronic Systems

Ø Missile and Other Weapon Systems

Ø Building Simulation and Test System Platforms