Domestic Virtual Instruments: Zynq-based Radar 10Gbps High-Speed PCIe Data Acquisition Card Solution (Part 2) Hardware Design

3.1 Introduction

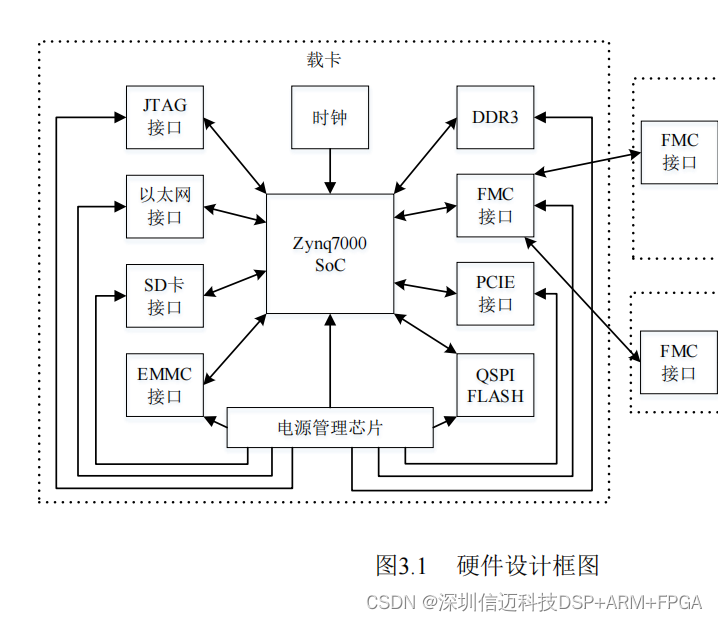

The hardware design of the acquisition card is fundamental to implementing its acquisition functions. A robust hardware design facilitates the implementation of acquisition features and simplifies software development. This chapter provides a detailed introduction to the acquisition card's hardware design, building upon the hardware design scheme presented in Chapter 2. This includes the selection, configuration, and specific circuit design of chips for both the carrier board and daughter cards. The overall block diagram for the hardware design of the carrier board and daughter cards is shown in Figure 3.1.

3.2 Carrier Board Hardware Design

3.2.1 Main Control Chip Selection and Configuration Circuit

(1) Main Control Chip Selection and Analysis

According to the analysis results of the acquisition card's hardware design in Chapter 2, the control chip must meet the following conditions:

The chip must include high-speed GTX interfaces, no fewer than 12 pairs, with 4 pairs for optical fiber and