RK3399+FPGA+MIPI Solution Details: subLVDS to MIPI Processing

#CROSSLINK Series #CROSSLINK vs XO3L

Overall, XO3L offers greater flexibility and is more akin to a general-purpose CPLD; CROSSLINK is more specialized.

For the requirement of converting subLVDS to MIPI, CROSSLINK has an advantage due to its higher integration, leading to greater stability.

#Key Points #CrossLink does not support JTAG download, requiring a separate download cable.

#IO Power-up Voltage IOs are low before program loading, or at least interpreted as low by the control logic.

#NVCM One-Time Programming (OTP)

If this one opportunity is used to configure the device to boot primarily from NVCM, subsequent operations will be limited to on-line debugging, and modifications to IO configurations will no longer take effect.

If this one opportunity is used to configure the device to boot primarily from NVCM, subsequent operations will be limited to on-line debugging, and modifications to IO configurations will no longer take effect.

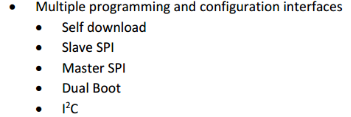

#Download Options

The actual flash used is MX25L1606EM1I-12G, but the options shown above are supported.

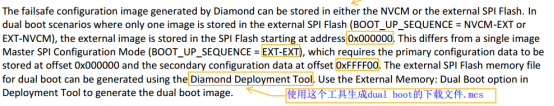

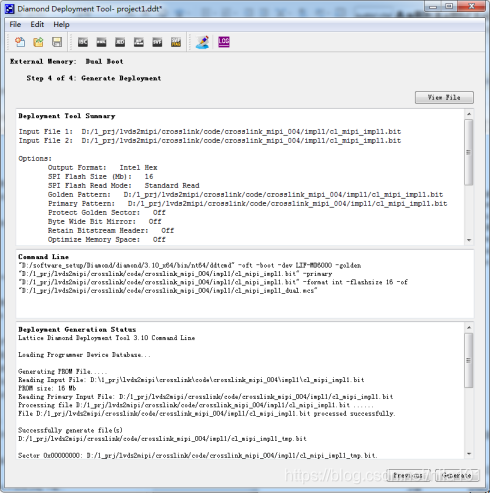

#Dual-Boot EXT-EXT External dual-boot method

#Internal Oscillator Can generate low-frequency LFCLKOUT=10KHz and one of the high-frequency HFCLKOUT options: 48M, 24M, 12M, or 6M, controlled by a division factor.

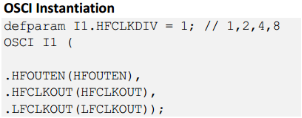

Use the following code for invocation, with the HFCLKDIV parameter for frequency division settings, and HFOUTEN: 1 to enable:

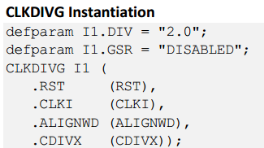

#Peripheral Clock Divider There are 4 dividers (2 in bank1, 2 in bank2) which can divide external input clocks by factors of 2, 3.5, 4, 7, and 8. The invocation code is as follows:

If using the dividers can meet the requirements, PLL resources can be saved.