Design and Implementation of an EtherCAT Master Based on ARM + FPGA

To address issues such as real-time performance and stability arising from the application of the real-time industrial Ethernet protocol EtherCAT to embedded master controllers, this paper first investigated the functional requirements of the EtherCAT master controller in an EtherCAT network control system. An architecture for implementing an embedded EtherCAT master was then analyzed and proposed. Subsequently, a hardware solution for implementing an EtherCAT master based on ARM + FPGA was designed for this architecture, along with a software implementation solution based on a real-time Linux operating system with Xenomai patches. Finally, an interconnected and interoperable testing platform was established. Experimental results demonstrate that this master controller exhibits compatibility with the EtherCAT standard protocol, extremely high real-time performance, and stability.

Real-time industrial Ethernet technology has evolved from conventional Ethernet technology. Because traditional Ethernet uses the CSMA/CD mechanism, it encounters real-time and stability issues when applied to industrial automation control systems [1-3]. Therefore, industrial Ethernets like EtherCAT, SERCOS, and other protocols [4-5] have been modified based on the traditional Ethernet communication model to achieve strong real-time performance and stability. These not only enable high-bandwidth transmission of large data volumes but also allow convenient access to Ethernet segments, achieving direct Ethernet connectivity to field-level control devices [6-7]. Due to its superior performance, EtherCAT is widely used in various automation control systems. Most EtherCAT master implementations are based on ordinary network interface card (NIC) devices, leveraging the real-time capabilities of system software to ensure the EtherCAT master's real-time performance, achieving microsecond-level real-time operation. Alternatively, the master can also be implemented using dedicated hardware, where the real-time characteristics of the hardware can achieve nanosecond-level real-time performance, along with higher stability [8-9].

This paper conducts an in-depth study on the implementation of real-time industrial Ethernet EtherCAT masters. It designs and implements a hardware and software solution based on an embedded ARM processor with an external dedicated master hardware FPGA, addressing technical challenges such as protocol compatibility, strong real-time performance, and high stability required by EtherCAT master controllers.

1 EtherCAT Master Control System

1.1 EtherCAT Control System

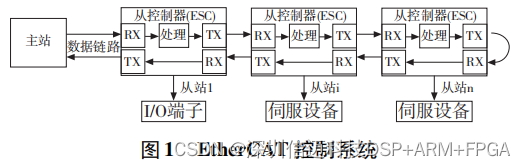

When the EtherCAT protocol is applied to industrial automation control systems, its control system structure is shown in Figure 1. The EtherCAT industrial Ethernet control system adopts a master-slave architecture [10]. The master station is the core of the entire network control system, responsible for scheduling data communication across the network. Slaves, as executive components of the EtherCAT control system, are distributed throughout the entire control system and can include types such as I/O terminals, servo drives, etc.

The EtherCAT master sends aggregated data frames, which sequentially pass through each slave. After very low-latency data upload and download operations, the slaves return the frames to the master. The master determines the status of the slaves based on the responses of the corresponding sub-telegrams, using this as input for network information management to prepare communication data for the next cycle. Concurrently, the EtherCAT master serves as the calling interface for the system's host computer, also providing different API function calling interfaces for various types of automatic control applications.

1.2 EtherCAT Master Controller Architecture

Based on the role of the EtherCAT master within the EtherCAT control system, it can be seen that, on one hand, the EtherCAT master is responsible for managing EtherCAT network information, and on the other hand, it is responsible for the API (Application Programming Interface) for data interaction with applications.