基于 ZYNQ 的四通道数据采集系统设计

针对接收设备普遍价格昂贵且集成度不够高的问题,设计一种基于低成本高集成度

的四通道 ADS⁃B 接收机。该设备在业内首先实现了低成本的实时信号采集、板上多频段 ADS⁃B

实时解码等功能于一体的四通道小型射频接收设备。设备以 ZYNQ⁃7000 系列芯片为主控芯片,

设计包含射频前端接收电路模块、信号采集电路模块、高速大容量的数据存储模块等,实现对

ADS⁃B 等目标信号的高速采样及处理。测试结果表明,该接收机可成功接收并解调 ADS⁃B 长报

文信号,为高性能数据采集及实时信号处理提供了一套低成本低功耗整体解决方案。

引 言

随着航空领域的快速发展,空域飞行的安全性

问题引起重视。在航空领域,广播式自动相关监视

(Automatic Dependent Surveillance⁃Broadcast,

ADS⁃B)是一种飞机在空中自动广播其位置、高度和

识别号等相关信息的航空电子技术[1] 。ADS⁃B 技术

方便相关人员对飞机状态进行管控,同时也可对附

近飞机进行避让,能极大地提升安全性和空域交通

效率。因此,飞行器上的接收设备能够接收针对

ADS⁃B 信号广播出来的飞机数据并解码出相关信

息就显得尤为重要[2] 。

目前在使用的接收设备如 RTL⁃SDR[3-4] ,虽然

价格低廉,但其只包含射频前端和 8 bit 的模数转换

器(Analog to Digital Converter,ADC),需 要 依 赖

PC 端来解调基带信号,该类设备存在实时性差、依

赖性强的问题;高度集成的接收机如 AD9371[5] 和

AD9361[6] ,其功能强大,接收信号范围高达 6 GHz,

但 仅 仅 针 对 ADS⁃B 信 号 接 收 ,AD9371 芯 片 和

AD9361 芯片价格较为昂贵且存在功能冗余。因

此,设计一种针对 ADS⁃B 信号的低成本且高度集成

的接收机是有必要的。

文中提出一种基于 ZYNQ 的四通道 ADS⁃B 信

号接收机,每通道采样率最高可达 40 MSPS,完成

从硬件电路板设计、逻辑控制到数据采集并处理的

一整套方案,能够高效且低成本地完成 ADS⁃B 信号

接收和处理,在航空领域中具有实际应用意义。

1 总体设计

1.1 接收架构

为了能够接收到 1 090 MHz 的 ADS⁃B 信号,接

收机在射频接收架构通常选择超外差式和零中频

式,其中超外差架构有易于设计且方便 AD 采样等

优点,但同时也有镜像干扰等问题;零中频架构虽

然不存在镜像干扰的问题,但有本振泄露、I/Q 不平

衡等缺点;但是这两种接收架构都不可避免地存在

I/Q 不平衡的问题,且 I/Q 采样需要两路 ADC,对硬

件性能要求更高,实际硬件比较难满足 I/Q 平衡和

正交的要求。

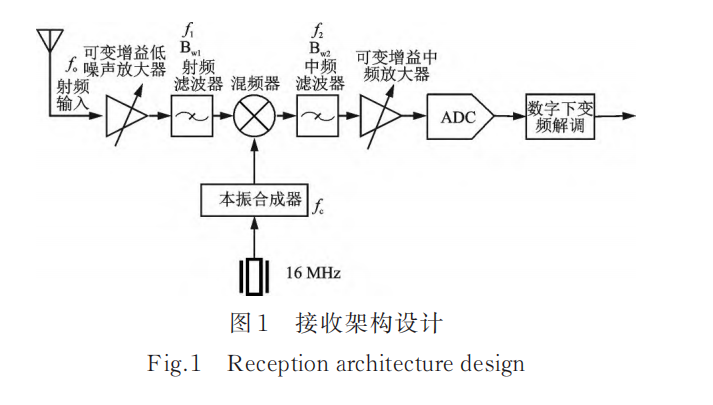

数字中频架构则可以避免以上问题。如图 1 所

示,数字中频接收机是在超外差接收机的基础上将

中频模拟信号采样,而后进行数字下变频解调出基

带信号,有效避免 I/Q 不平衡问题。除此之外,滤波

器完成中频滤波相对更容易,可降低滤波器的 Q 值

要求,系统硬件成本更低。

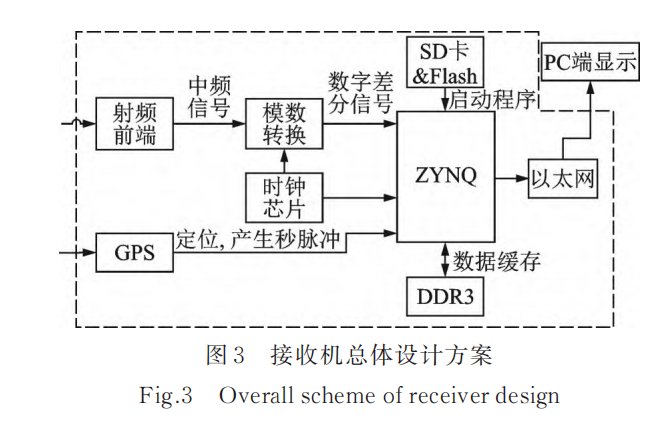

1.3 总体设计方案

接收机的总体设计方案如图 3,系统总体主要

由 ZYNQ⁃7000 主控模块、射频接收模块、ADC 模

块、存储模块、时钟模块等模块组成。系统主控芯

片为 ZYNQ⁃7000 系列芯片,负责总体的逻辑控制

和数据处理,通过射频调谐器接收 ADS⁃B 信号,而

后下变频得到中频信号,模数转换器实现对中频信

号的高速采样[9] ,采样率最高为 40 MS/s,时钟芯片

为 ADC 芯片提供多种可选时钟输入,同时为主控

芯片提供时钟输入。为满足采集数据实时存储的

要求,设计了高速、大容量的 DDR3 硬件电路,SD 卡

存储启动程序。ZYNQ 模块数据处理完成后可通

过以太网接口上传至 PC 端,PC 端只负责显示,无

需处理数据,大大提高了接收机的实时性,降低了

对 PC 端的依赖。

2.2 射频模块设计

从天线接收载波频率为 1 090 MHz的 ADS⁃B 射

频信号,信号经过长距离的传输会衰减,天线接收到

的信号比较微弱,因此将信号输入低噪声放大器放

大,而后输入至射频带通滤波器滤除杂波和镜像干

扰,由本振生成电路产生本振信号,将放大滤波后的

信号和本振信号一起输入至混频器混频,继而进入

中频滤波器中滤波,再进入中频放大器放大功率,中

频放大器提供了接收机的灵敏度与选择性。后续的

处理都是在中频中进行,处理的成本也更低。

通过图 1 设计,成功摆脱了对外部表面波过滤

器、外部 LNA、巴伦变压器和低压差线性稳压器的

依赖,在后续应用中既保证性能又控制成本最低,

同时具备更大的灵活性。内部引入射频自动增益

控制以确保最佳信噪比和最小信号失真,内嵌智能

功率探测器适应不同输入功率场景,优化射频性

能,提供特殊的无杂散动态范围。在实际应用中,

随着射频输入功率变化,内部功率检测器自动调整

LNA 增益,保持最佳水平,确保在各工作环境下始

终提供最佳中频输出信号质量。

在高速信号的接收系统中,射频前端的输入电

路设计是非常重要的,需要考虑阻抗匹配、噪声抑

制等,所以在印刷电路板(PCB)设计中,四个通道

射频输入线路端采用 70 Ω 阻抗匹配。射频接收模

块在系统应用中能够实现低功耗、高射频性能,在

射频灵敏度、线性度、相邻通道抗干扰等方面提供

了优越的性能。

2.3 ADC 模块电路设计

基于分析将 ADC 采样率设为 24 MHz,ADC 模

块 选 用 的 是 AD9219 芯 片 ,采 样 率 最 高 可 达 40

MSPS,完全能够满足要求,而且芯片内置多种功能

特性,保证灵活性并降低系统成本,满足四通道要

求,在成本更低的条件下保证足够的采样率。

4 系统测试与验证

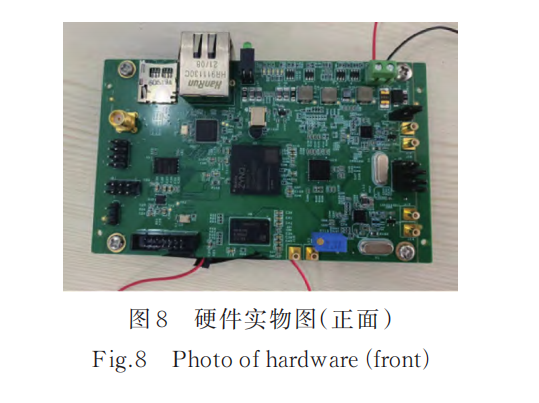

ADS⁃B 信号数据采集系统硬件实物图正面如图

8 所示,是一个 10 cm×6.9 cm 的八层 PCB 板。总体

芯片成本较低,是一种小体积、低成本的设计方案。

验证该接收机的功耗,可调电源提供 5 V 电压,

额定电流 1 A,经过 8 h 测试,测得接收机功耗不大

于 4 W。相比于其他 ADS⁃B 接收机如文献[14]中的

功耗不大于 5 W[14] ,功耗小了 20%。

验证接收机能否接收实时 ADS⁃B 信号,将接收

机 实 时 采 集 到 的 数 据 处 理 后 发 送 到 PC 端 ,通 过

Matlab 显示。图 9 所示为实时接收到的信号,把认

为是 ADS⁃B 的信号用“*”标识。分析其中一个“*”

号的信号解调后是 120 µs 的长报文 ADS⁃B 信号,报

头和报文如图 10 所示。证实本系统可以成功接收

实时 1 090 MHz 的 ADS⁃B 信号。