全国产PCIE 4.0 接口信号完整性仿真分析,以万兆网卡和11槽PCIe GPU底板(PCIe 4.0/5.0)为例

万兆网卡设计中 PCIE 4.0 接口信号完整性仿真分析

由于目前已有的 PCIE 接口信号完整性仿真精度和可靠性较低,建立了一种新的 PCIE 4.0 信

号通道链路模型和仿真分析方法。通过仿真软件 POWERSI 对万兆网卡 PCB 建立×4 PCIE 4.0 信号通

道链路模型;利用已建立的模型在 ADS 软件中进行时域、频域和回环仿真;对仿真得到的回波损耗、

插入损耗和眼图进行分析,判断 PCIE 4.0 信号走线是否满足设计要求。通过该方法得到的 8 对 PCIE

4.0 差分信号的回波损耗均小于-6 dB,插入损耗均大于-28 dB,眼图的眼宽和眼高均大于 0.3 UI 和

15 mV,满足 PCIE 4.0 协议规范的要求,与已有的仿真结果相比,该方法的可靠性更高

集成电路的迅猛发展导致信号上升时间减少,时

钟频率增加,进而出现信号不完整的现象,此现象带

来的严重后果是电路不能正常工作[1]。为了消除此现

象,国内外相关领域的专家纷纷致力于研究信号完整

性问题[2-7]。

从 PCIE 1.0 到现在的 PCIE 5.0,总线频率和传输

速率在成倍增加,因此信号在传输的过程中会出现信

号不完整的现象[8]。为了解决此问题,国内外学者进行

了一系列的研究。文献[9]利用仿真软件 Allegro Sigrity

对 PCIE 2.0 差分信号进行时域分析,得到其眼图,根

据输入眼图与输出眼图的差异来判断 PCIE 2.0 差分

信号的质量,此仿真分析方法的缺点是只单纯地对

PCIE 差分信号进行时域分析,而且输入、输出眼图之

间的差异容限范围也没有评判标准,因此得到的仿真

结果可靠性较低。文献[10]利用仿真软件 Hyperlynx 对

PCIE 2.0 信号进行时域与频域分析,得到回波损耗、插

入损耗和眼图,通过与协议规范的对比来评判 PCIE

的信号质量,此仿真分析方法能较好地评判出 PCIE

的信号质量,但是没有考虑到 PCIE 信号更长链路时

的传输情况,因此得到的结果可靠性并不高。针对以

上问题,本文提出了一种新的 PCIE 4.0 信号完整性仿

真分析方法,建立了万兆网卡 PCB ×4 PCIE 4.0 信号通

道链路模型,考虑到 PCIE 信号更长链路时的传输情

况,在原有的时、频域分析的基础上又添加了回环分

析,提高了仿真结果的可靠性。

2

万兆网卡的设计方案

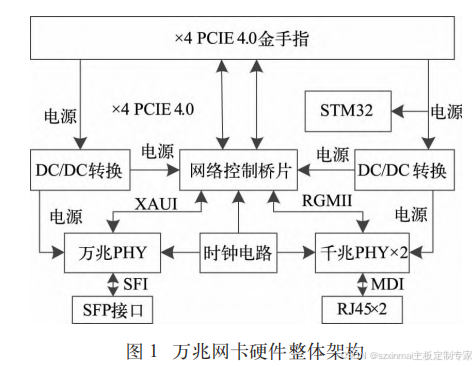

本文提出的万兆网卡硬件整体架构如图 1 所示,

它主要由网络控制桥片、电源模块、时钟电路、万兆

PHY 模块、千兆 PHY 模块组成。其中,网络控制桥片

采 用 Intel 公 司 的 E810XXVDA, 万 兆 PHY 采 用

Microsemi 公司的 VSC8486,千兆 PHY 采用 Marvell

公司的 88E1111。该网卡通过 PCIE 接口实现网口的扩

展功能。

3

接收端和信道的设计要求

从 PCIE 4.0 协议规范[11]可知,其接收端和信道需

符合一定的设计要求。

图 1 万兆网卡硬件整体架构

3.1 接收端的设计要求

PCIE 高速串行信号从发送端发送,经过信道到达

接收端,在此过程中信号会有一定的衰减,进而会发

生失真现象。对于接收端信号质量的鉴定方法有 2 种。

第一种是传统时域瞬态仿真法,该方法的缺点是仿真

速度慢、精度低和可靠性差;第二种方法是统计眼图

法[12],该方法的优点是仿真速度快、精度高和可靠性

高。经综合考虑,本文采用第二种方法来鉴定接收端

的信号质量。眼图有 2 个参数,分别为眼宽和眼高,只

有满足最低的眼宽和眼高,该信号才可通过,否则不

可通过。PCIE 4.0 协议规范规定接收端信号眼图的眼

宽至少为 0.3 UI,眼高至少为 15 mV,当满足以上 2 个

条件时,接收端的 PCIE 信号质量才合格,反之则不合

格。时域仿真中得到的信号眼图都以这 2 个参数为评

判标准,判断接收端 PCIE 信号质量是否合格。

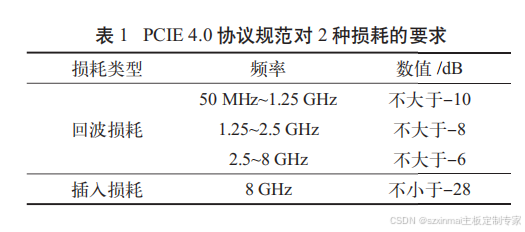

3.2 信道的设计要求

高速信号在信道中传输因受反射、衰减等的影

响,会有一定损耗[13]。由反射所导致的损耗称为回波损

耗,由衰减所导致的损耗称为插入损耗[14]。在信号的传

输中,由于阻抗不连续,导致反射现象出现,反射会导

致信号失真,表现方式为振铃、上冲和下冲等。衰减现

象的出现会导致信号质量退化,表现方式为信号上升

沿退化和幅度降低等。回波损耗一般用 S11 表示,插入

损耗用 S21 表示,S11 越小,说明信号在阻抗不连续点反

射得越少,即有用的信号反射越少,S21 越大,说明有用

的信号在接收端保留得越多,即有用的信号衰减越

少。PCIE 4.0 协议规范对回波损耗和插入损耗的要求

如表 1 所示。频域仿真中得到的回波损耗和插入损耗

都以表 1 中的值为评判标准,来判断信道中 PCIE 信

号质量是否合格。

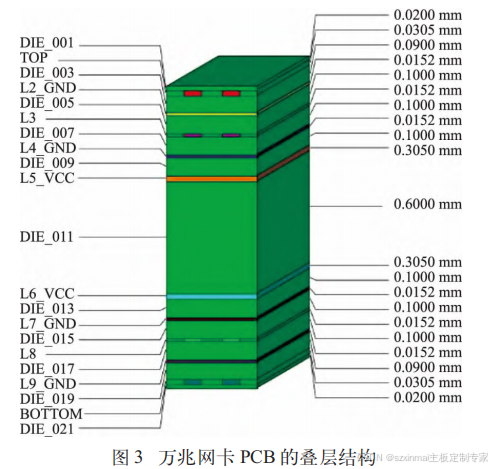

4 PCIE 4.0 接口信号完整性仿真分析

PCIE 4.0 信号传输速率为 16 Gbit/s,基本频率为

8 GHz,因此对于该信号的布线不能再像低速信号布

线那么随意,需进行信号完整性仿真分析。本文主要

对万兆网卡 PCB 的 PCIE 4.0 信号走线进行信号完整

性仿真分析。

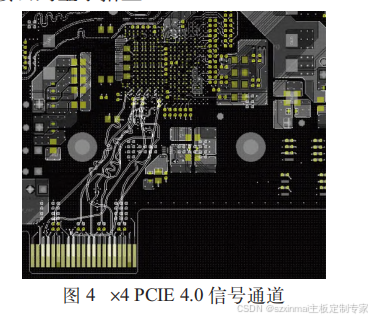

4.1 仿真分析流程设计

设计的 PCIE 4.0 接口信号完整性仿真分析流程

如图 2 所示。首先,将初步设计的 PCB 用 Allegro

Sigrity 中的 SPDLinks 转换程序转换成 SPD 文件;然

后,将转换后的 SPD 文件导入到仿真软件 POWERSI

中,建立×4 PCIE 4.0 信号通道链路模型,通过仿真得

到该模型的 S 参数;接着将得到的 S 参数导入到 ADS

软件中进行频域、时域与通道回环仿真分析,得到回

波损耗、插入损耗和眼图;最后,根据 PCIE 4.0 协议规

范来判断其是否满足要求,若满足要求则仿真通过,

否则仿真不通过。

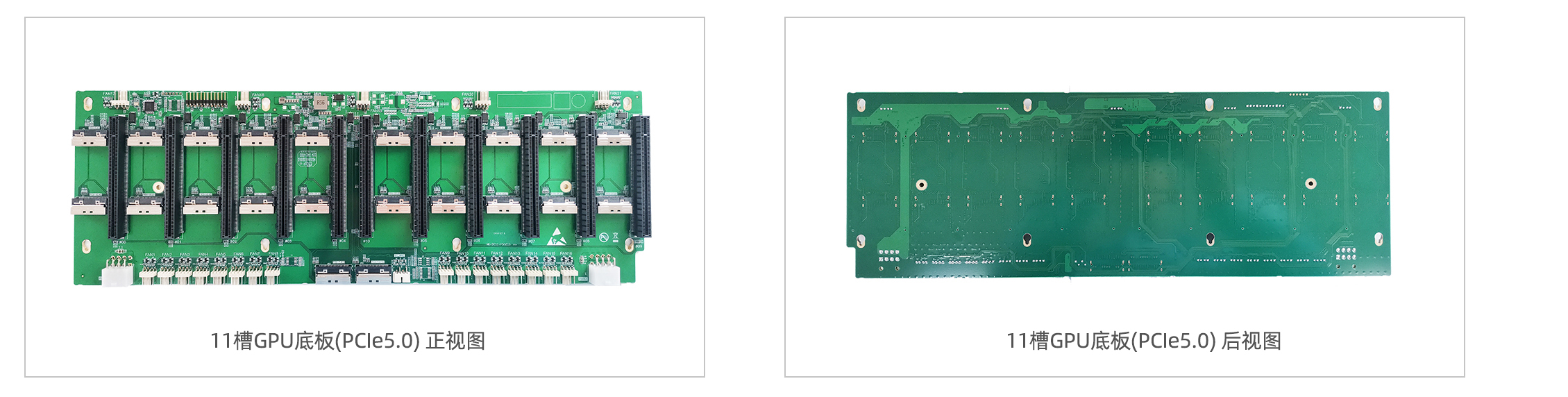

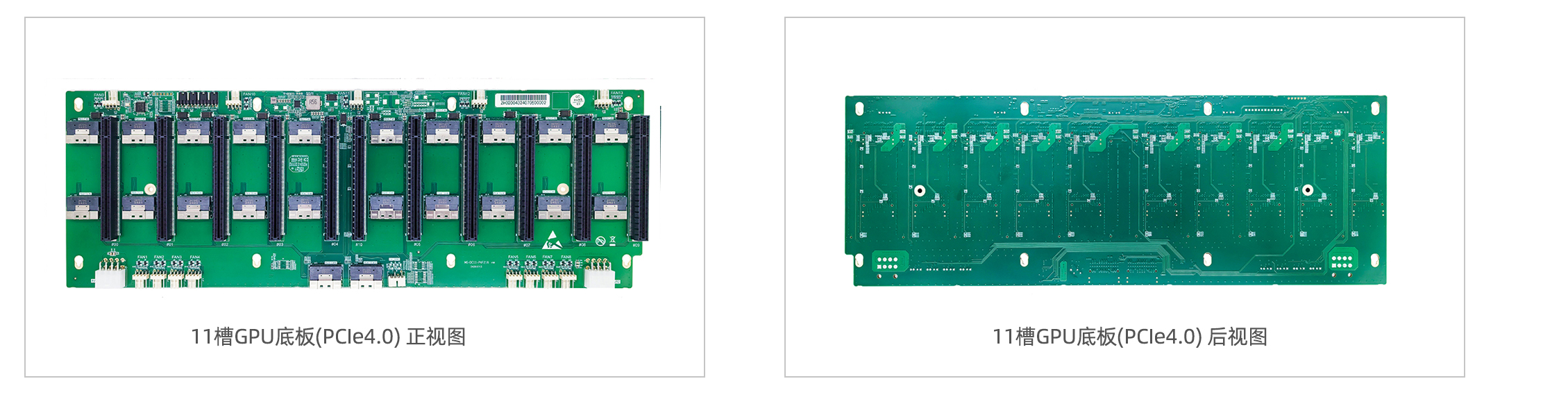

==========全国产11槽PCIe GPU底板(PCIe 4.0/5.0)设计方案,支持定制========

*10槽双宽和1槽单宽;

*11槽PCIe*5.0GPU底板;;

*每个槽采用MCIOx8*2或SFF8654x8*2

11 槽 PCIe5.0 GPU Baseboard搭配22个MCIOx8接口,PCIe5.0 x16 带宽,速率高达32GT/ s ,支

持10槽双宽和1槽单宽。Baseboard提供了2* CPU 8Pin 电源 接⼝、21* 4针风扇接口、1* IPMB接口等。

MG-DC11-P5G216-V10产品特持PCIe5.0,兼容各 类 的HBA卡、Retimer卡。

支持PCIe4.0,兼容 PCIe 3.0 以及PCIe 2.0,同时对各类的HBA卡、Retimer卡、具有良好的兼容性。

功能特性

产品规格

11槽 GPU底板(PCIe 5.0)

11槽 GPU底板(PCIe 4.0)

型号

MG-DC6-P5F216_V10

MG-DC6-P4F216_V10

输入接口

22*MCIOx8 PCIe5.0

22*SFF8654 PCIe4.0

PCIe插槽数

11* PCIe5.0 x16

电源接口

2* GPU 8PIN

IPMB接口

4Pin BMC I2C

尺寸

426(长) x 145(宽) x 2.5(高) (mm)

☑深圳信迈支持OEM/ODM定制服务